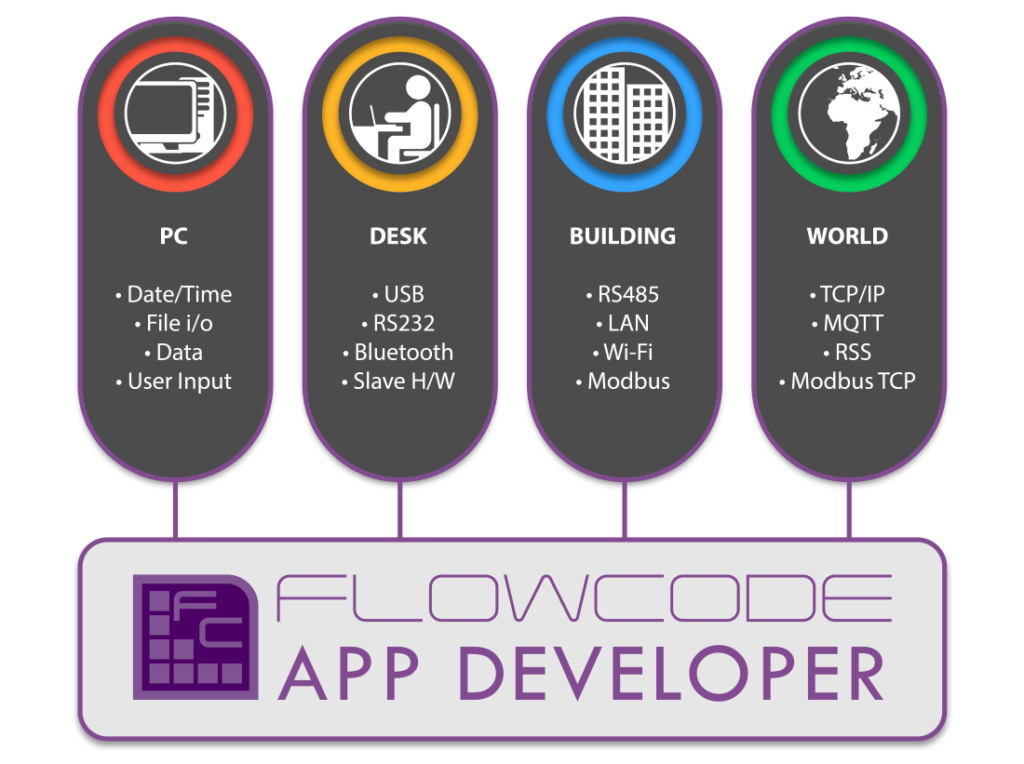

Sur cette page, nous avons développé un certain nombre de programmes gratuits App Developer qui sont des dispositifs/systèmes utiles en eux-mêmes. Il existe de nombreuses utilisations de App Developer mais pour commencer, nous nous sommes concentrés sur le test : nous voulons vous fournir une gamme d’applications vraiment excellentes pour vous permettre de créer un superbe environnement de test basé sur PC pour le développement de produits électroniques et pour le test en usine et à la maison.Vous n’avez pas besoin d’une copie d’App Developer pour profiter de ces applications. Les interfaces de programmation d’applications et la version exécutable des programmes vous permettent de les exécuter à partir de n’importe quel PC ou tablette Windows en utilisant le matériel peu coûteux fourni. Bien entendu, nous serions ravis que vous achetiez une copie d’App Developer et que vous personnalisiez les applications pour votre propre usage.

Chacun de ces projets a une section dans notre Forum où vous pouvez poster des questions et des améliorations que vous avez apportées.

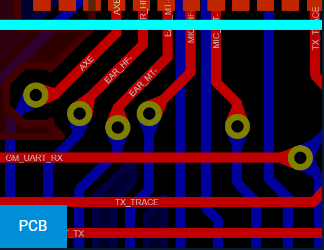

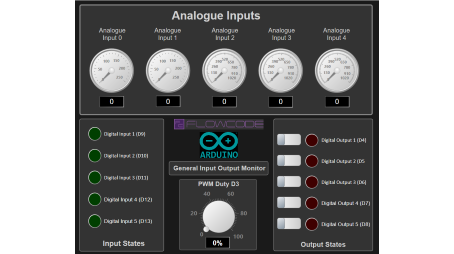

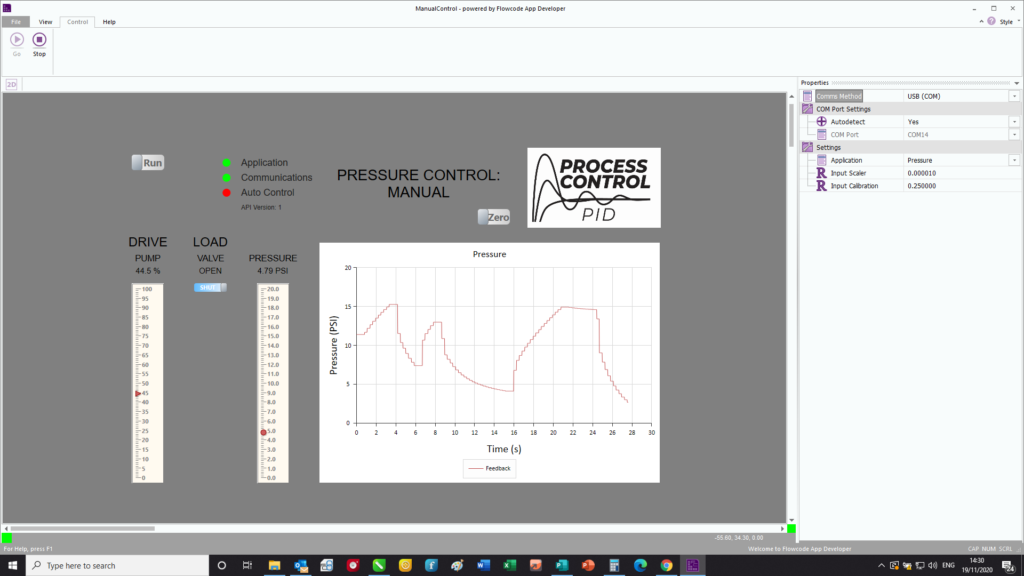

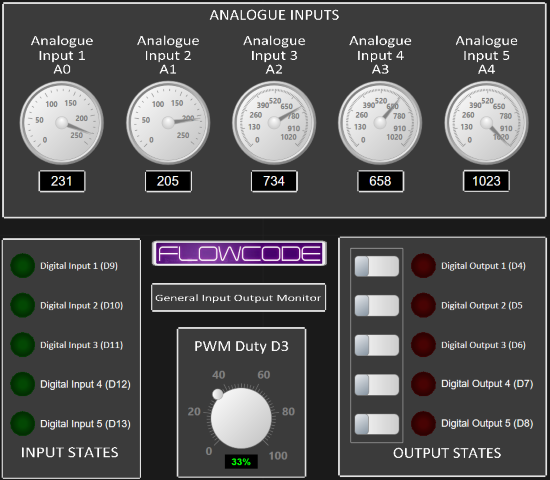

Utilisation générale : carte E/S – Arduino, USB

|

Matériel : Arduino

Connexion : USB

Description : un projet d’E/S à usage général avec 5 entrées analogiques, 5 entrées numériques, 5 sorties numériques, et une commande PWM à un seul canal. |

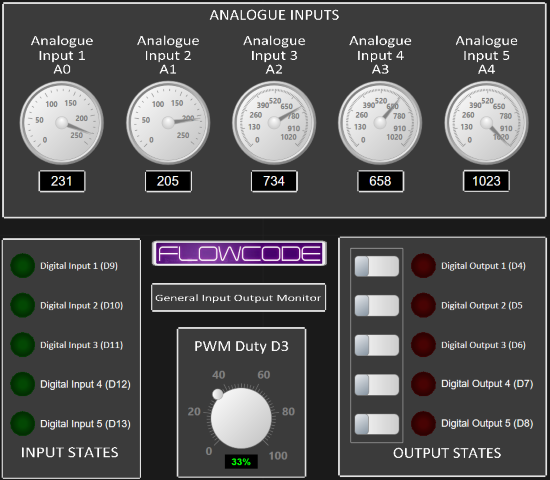

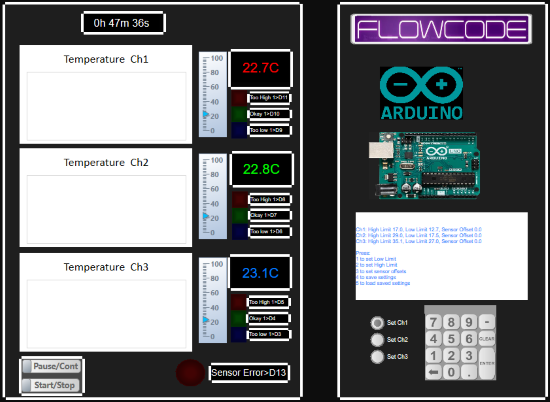

Enregistreur de température à trois canaux – Arduino, USB

| Matériel : Arduino Uno

Connexion : USB

Description : un enregistreur de température à trois canaux utilisant de simples thermistances sur un Arduino Uno avec graphique intégré et enregistrement dans un fichier CSV externe. |

|

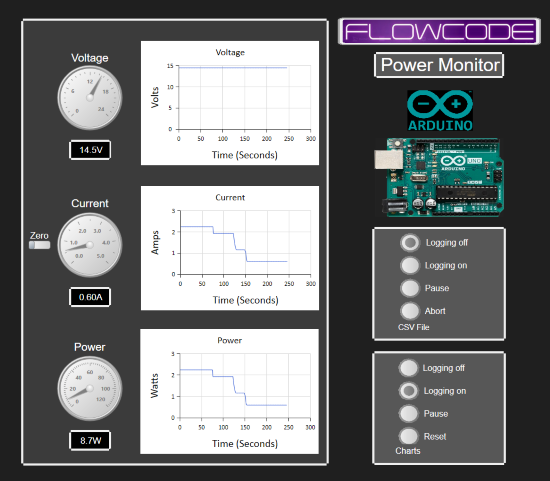

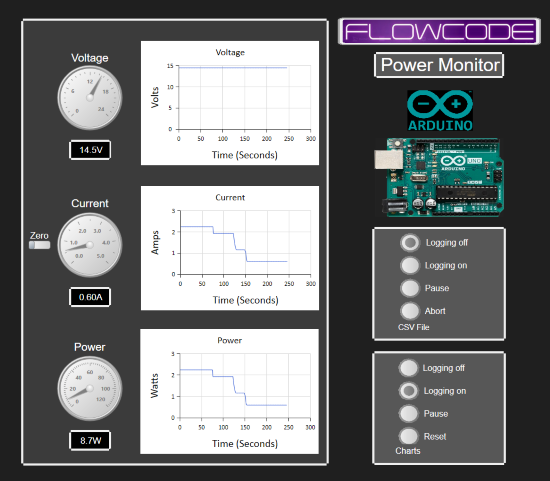

Moniteur de puissance – Arduino, USB

|

Matériel : Arduino

Connexion : USB

Description : Il s’agit d’un moniteur d’alimentation d’usage général pour un Arduino Uno qui utilise un capteur de courant SparkFun breakout ACS723 (SEN-13679). |

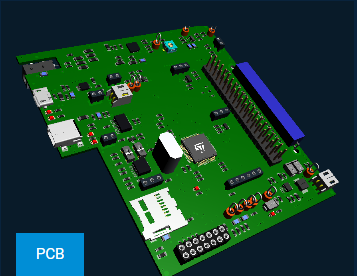

Utilisation générale : Carte E/S – PIC, USB

| Matériel : PIC basé sur le 18F4455 – compatible avec Matrix ECIO

Connexion : USB

Description : un projet d’E/S à usage général avec 5 entrées analogiques, 5 entrées numériques, 5 sorties numériques, et un contrôle PWM à un seul canal. |

|

Utilisation générale : Carte E/S – ESP32, USB

|

Matériel : Carte ESP 32 – xxxxxx

Connexion : USB

Description : un projet d’E/S à usage général avec 5 entrées analogiques, 5 entrées numériques, 5 sorties numériques, et un contrôle PWM à un seul canal. |

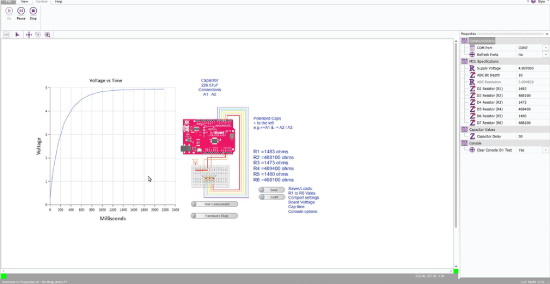

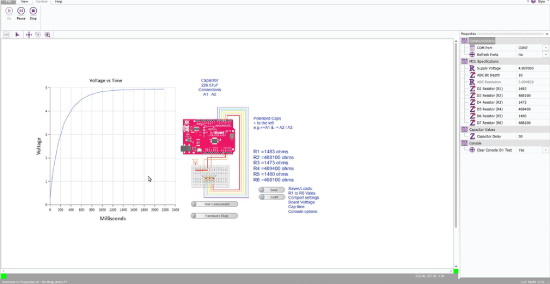

Testeur de composants – Arduino, USB

| Matériel : Arduino Uno – Nécessite une planche à pain et plusieurs résistances

Connexion : USB

Description : ce projet fantastique utilise un Arduino Uno avec 5 résistances externes pour vous fournir une installation de test pour les résistances, les condensateurs, les inductances, les transistors et les diodes. Le programme vous indiquera la valeur, si le composant fonctionne ou non, et vous indiquera même les connexions du transistor ou de la diode. |

|