Multipower

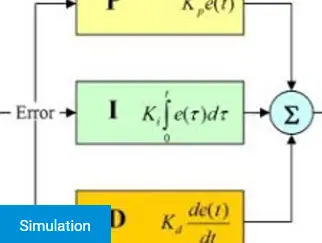

Découvrez comment l’algorithme PID (Proportionnel-Intégral-Dérivé) optimise la précision des systèmes dans divers domaines.

Communication SPI

Introduction

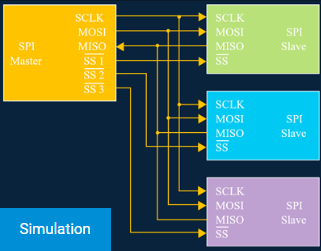

SPI, ou Serial Peripheral Interface, est un des plus populaires protocoles de communication implémenté sur les microcontrôleurs. Il est couramment utilisé pour interagir avec des périphériques (capteurs, afficheurs, etc).

SPI est un protocole de communication synchrone, ce qui signifie qu’il existe une ligne horloge dédiée (voir les protocoles de communication synchrones/asynchrones). Les liens de communications du SPI sont :

- MISO = Master In Slave Out

- MOSI = Master Out Slave In

- SS = Slave Select

- SCK ou SCLK = Serial Clock

A la lecture des noms on voit qu’il existe un composant maître (MASTER) et un composant esclave (SLAVE). Le maître est le composant qui contrôle le lien horloge, donc c’est lui qui contrôle la communication.

SPI est un protocole « full duplex », car deux liens de données existent – un pour chaque direction de communication (master vers slave et slave vers master). Il est ainsi possible d’envoyer et de recevoir des données en même temps.

Le bus SPI

Plusieurs modules esclaves peuvent être connectés au même maitre avec les mêmes liens de communication SCK, MISO et MOSI (appelés bus SPI). Un lien distinct « Slave select » (SS) est toutefois nécessaire pour chaque esclave ; le maitre active les liens Slave Select (qui est actif à l’état bas – c.a.d. bas pour sélectionner et haut pour désélectionner) en fonction de l’esclave avec lequel il souhaite communiquer.

En pratique il est rare que des données soient à la fois transmises et reçues en même temps (le scénario habituel est qu’une instruction soit suivie d’une réponse, ou juste que le maître lise l’état de l’esclave). Cependant un des avantages du SPI est qu’il est simple à déboguer et dépanner (avec un oscilloscope par exemple) car on dispose de liens de communication dédiés. Les protocoles tels que I2C nécessitent moins de lignes mais sont plus difficiles à dépanner du fait leur complexité. Un autre avantage du SPI est que toutes les lignes de communication sont actives à l’état haut ou bas. Par opposition, par exemple, à l’I2C dont les liens de communication sont uniquement pilotées à l’état bas et des résistances de tirage sont utilisées pour les mettre à l’état haut lorsqu’elles ne sont pas actives (voir notre article sur le bus I2C). Comme les lignes sont toujours actives, cela signifie qu’il est possible d’obtenir des débits de données supérieurs. |

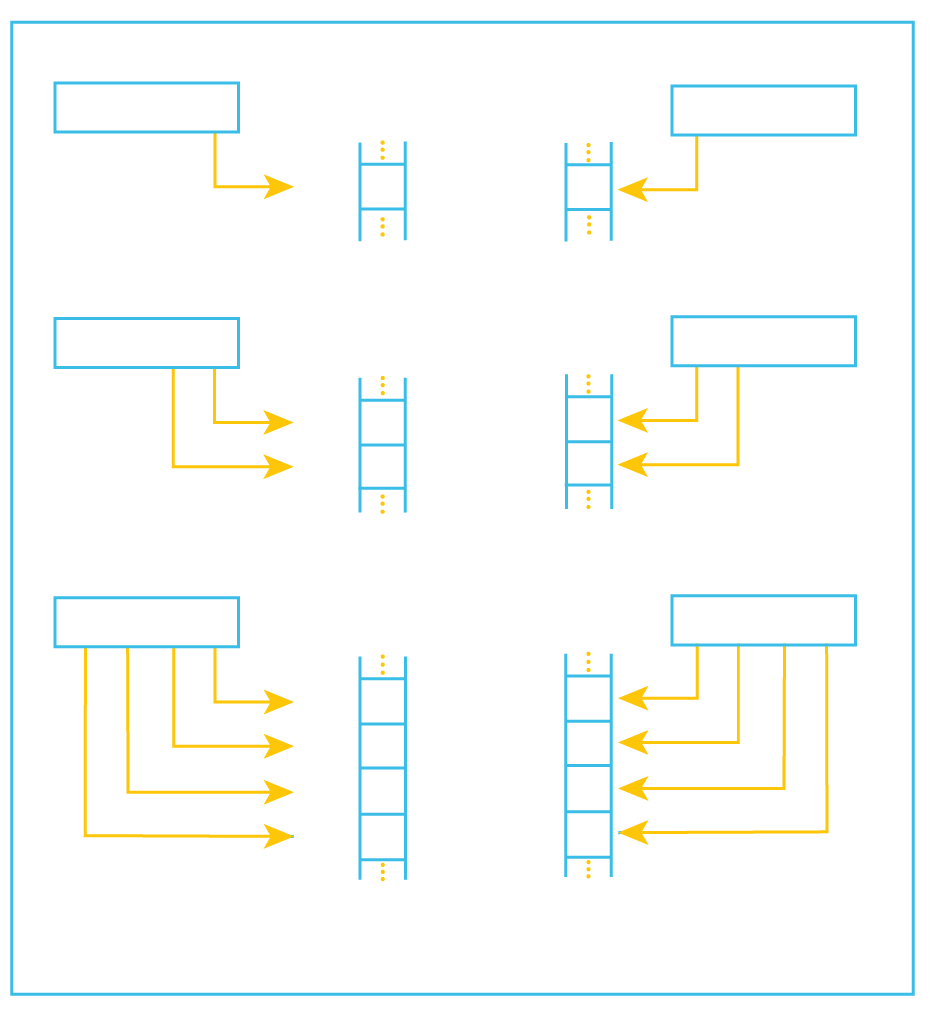

Dual et Quad SPI

Il existe des variations du SPI appelées Dual et Quad SPI, lorsque plus d’un lien de données est utilisé pour transmettre des données dans une direction en même temps (techniquement en parallèle), ce qui accroit le débit (la vitesse de communication). Ces variantes sont populaires, par exemple dans les composants mémoire FLASH qui nécessitent un débit important. Dans un Dual SPI la communication débute Off comme pour le Single SPI, cependant elle peut passer en Dual mode après qu’une commande soit envoyée au module esclave (voir la documentation du composant esclave). En mode Dual, les liens MISO et MOSI (half duplex) deviennent bidirectionnels, de nom SIO0 (Serial I/O 0) et SIO1. Pour chaque octet, les bits pairs sont transmis sur SIO0 et les bits impairs sur SIO1.

Le Quad SPI est similaire, excepté qu’il existe deux liens de communication supplémentaires (SIO2 et SIO3), et que la moitié d’un octet est transmis à la fois.

Configuration SPI

Certains paramètres du protocole SPI sont configurables, tels que la façon dont la donnée est émise/reçue ou si l’horloge est inactive à l’état haut ou bas. Il est aussi possible de configurer si la donnée est transmise avec le LSB ou le MSB en premier – habituellement le MSB en premier est utilisé.

Si vous n’êtes pas familiers avec les termes LSB et MSB, lisez notre article Signification de bit & Endian.

Regardez la bibliothèque des exemples de projets Proteus pour charger des exemples sur la communication avec des capteurs SPI ainsi que sur l’utilisation générale du protocole avec divers microcontrôleurs.

Copyright Labcenter Electronics Ltd. 2024

Traduction française

Copyright Multipower France 2024

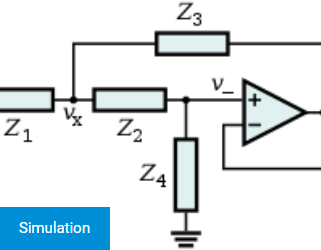

Cet article traite des avantages d’ajouter des composants actifs pour filtrer un signal.

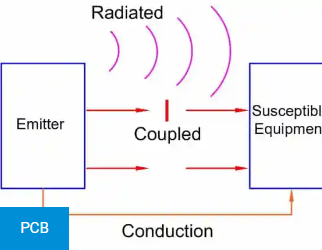

Découvrez des conseils essentiels pour éviter les problèmes d’EMI et EMC tout en optimisant la performance de vos conceptions PCB.

Protocoles synchrones vs asynchrones

Introduction

Vous avez peut-être déjà entendu parler des protocoles de communication synchrones et asynchrones (tel que UART – Universal Asynchrone Receiver and Transmitter), mais savez vous de que signifient ces termes ? Si ce n’est pas le cas, ne vous inquiétez pas car nous allons en parler dans cet article.

En communication numérique – lorsque nous souhaitons envoyer des données entre un appareil et un autre – nous devons piloter des liens de communication de données soit à l’état Haut (1 – HIGH) soit à l’état Bas (0 – LOW). Ce sont les seules options disponibles. Supposons que nous voulions envoyer la donnée ‘Hello’ d’un appareil à un autre. Si nous utilisons le codage ASCII (pour lequel chaque lettre de l’alphabet est représenté par un nombre, car les ordinateurs travaillent en interne uniquement avec des nombres), ceci serait représenté par la séquence de nombres.

72 101 108 108 111

ou en binaire

01001000 01100101 01101100 01101100 01101111

Voir notre article sur les systèmes de numération pour plus d’information.

Si nous ne disposons que d’une seule ligne de données (comme c’est le cas pour la plupart des protocoles de communication) alors nous pouvons émettre un bit après l’autre, en pilotant la ligne de données entre les états haut et bas conformément à la valeur du bit à envoyer (les couleurs ont été ajoutées pour faciliter la lecture, sachant que les données binaires n’ont pas de couleurs !) avec le LSB transmit en premier (Bit le moins significatif – Least Significant Bit).

Le LSB d’un nombre binaire est le bit de plus petite valeur (le plus lointain sur la droite) et le MSB (Most Significant Bit) est le bit de plus grande valeur (le plus à gauche). Voir notre article sur la signification de Bit & Endian

Interpréter les données

Si les données transmises étaient toujours une séquence alternée de 1 et de 0, il serait assez facile de les interpréter car le motif est régulier et prévisible :

mais évidemment ce n’est pratiquement jamais le cas. Que se passerait il pour la séquence de 4 x 1 suivie de 4 x 0 (11110000) ?

Sans information supplémentaire le récepteur pourrait dire que le signal était 10, 1100, 111000 ou 11110000 (ou 1111100000, et ainsi de suite). Il nous faut absolument quelque chose en plus pour clarifier la communication.

Synchrone ou asynchrone

Cela se résout soit avec une ligne de communication supplémentaire pour indiquer le timing de chaque bit sur la ligne de données, ou en permettant au récepteur de connaître en interne la durée de chaque bit sur la ligne de données. La première possibilité, où une ligne de communication supplémentaire est utilisée pour indiquer les timings de chaque bit, est appelée communication synchrone. La ligne supplémentaire dans la communication synchrone est appelée la ligne d’horloge (parce que les horloges sont utilisées pour chronométrer les choses). La deuxième possibilité, où le récepteur connaît en interne la durée de chaque bit sur la ligne de données, est appelée communication asynchrone. Avec la communication asynchrone, le récepteur et l’émetteur ont besoin d’une horloge interne précise pour mesurer le temps. Le récepteur et l’émetteur doivent également évidemment être réglés pour utiliser la même vitesse/timing (taux de bauds) afin de communiquer avec succès.

La transmission synchrone par rapport à la transmission asynchrone se résume donc à savoir si l’horloge est externe (synchrone) ou interne (asynchrone). Quelques exemples de protocoles asynchrones comprennent UART, USB, CAN et Ethernet. Quelques exemples de protocoles synchrones comprennent SPI, I2C et DDR.

Avantages et inconvénients

Un avantage des protocoles synchrones est qu’ils ne nécessitent pas que le dispositif ait une horloge interne très précise (plus la communication est rapide, plus l’horloge interne devrait être précise). En conséquence, les protocoles de communication synchrones sont souvent utilisés dans de petits périphériques peu coûteux tels que des capteurs. Un autre avantage des protocoles synchrones est que les deux côtés de la communication n’ont pas besoin de connaître à l’avance quel sera le débit de données (timing). Certains protocoles synchrones ont même des débits de données variables et/ou peuvent utiliser la ligne d’horloge pour indiquer qu’ils sont toujours occupés en la maintenant dans le même état jusqu’à ce qu’ils soient prêts à recevoir de nouvelles données (c’est une fonctionnalité de l’I2C) ; les protocoles asynchrones nécessitent une ligne de communication supplémentaire pour implémenter cette fonctionnalité (comme la ligne CTS/RTS dans UART).

Un avantage des protocoles asynchrones est qu’ils nécessitent moins de lignes de communication et, de ce fait, ils génèrent moins de bruit électromagnétique (voir notre article sur les interférences EMI/EMC).

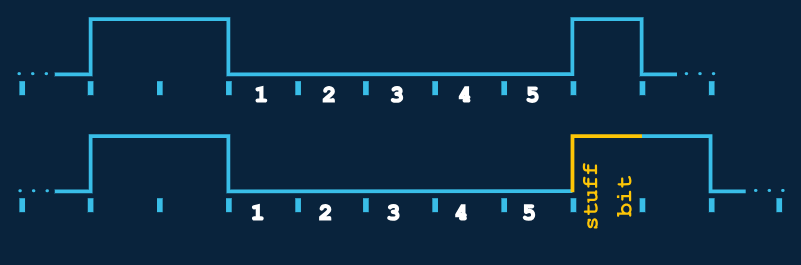

Comme il peut être difficile avec les protocoles asynchrones d’obtenir une synchronisation parfaite des horloges des deux côtés, généralement ils nécessiteront de temps en temps au moins une transition sur la ligne de données afin de réaligner leurs horloges internes. Cela peut faire partie de la trame du protocole (comme avec UART), ou cela peut être mis en œuvre en exigeant l’insertion d’un bit de bourrage (stuff bit) de polarité opposée après un certain nombre de bits consécutifs de la même polarité (le bit de bourrage est éliminé lors du décodage du protocole, comme avec le protocole CAN).

Résumé

C’est tout ce qu’il y a à comprendre dans les termes de communication synchrone ou asynchrone.

- Synchrone = Horloge externe

- Asynchrone = Horloge interne

Proteus inclut dans ses bibliothèques de nombreux composants modélisés utilisables en simulation, que ce soit pour les protocoles synchrones ou asynchrones. De plus, il existe également des instruments virtuels qui supportent ces protocoles de communication.

Copyright Labcenter Electronics Ltd. 2024

Traduction française

Copyright Multipower France 2024

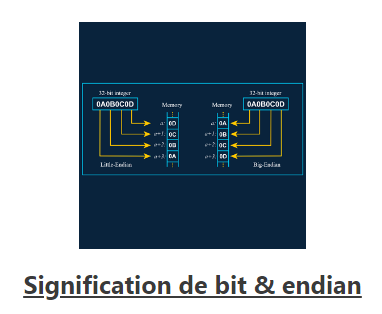

Signification de bit & endian

Introduction

Cet article suppose que vous êtes familier avec les systèmes de numération (Décimal / Hexadécimal) – si ce n’est pas le cas, veuillez commencer par lire l’article sur ce sujet.

En informatique, la plus petite unité de nombre est généralement l’octet (Byte – 8 bits). Techniquement la plus petite unité est le bit (1 ou 0, Vrai ou Faux), mais en terme de représentation c’est l’octet que constitue le plus petit bloc de base. Des nombres plus grands sont construits en utilisant plusieurs octets et les protocoles de communication utilisent typiquement l’octet comme la plus petite unité pour transférer des données.

Signification des bits

Par exemple, si nous considérons le nombre binaire ‘10000001’, alors les bits aux deux extrémités de la séquence binaire ont des noms spéciaux – le bit à l’extrême droite s’appelle le LSB (Least Significant Bit – Bit de moindre poids) et le plus à l’extrême gauche s’appelle le MSB (Most Significant Bit – Bit de poids le plus élevé).

Le listing des bits dans un octet illustre le MSB et le LSB. Le bit le plus à droite a la valeur décimale 1 et le bit le plus à gauche a la valeur décimale 128 (donnant ainsi la valeur totale de 129 à cet octet) – le bit de gauche a la plus grande valeur (la plus élevée) et le bit de droite a la plus petite valeur (la moins élevée).

Avec les protocoles de transmission de données série, les données peuvent être transmises soit en commençant par le LSB, soit en commençant par le MSB. Les protocoles USB et UART transmettent le LSB en premier alors que les protocoles I2C et CAN transmettent le MSB en premier. Le SPI peut être configuré pour utiliser l’une ou l’autre option, mais généralement, c’est le MSB qui est utilisé.

Exemple de communication UART – LSB en premier

Exemple de communication I2C – MSB en premier

Endian

Lorsque plusieurs octets sont combinés en mémoire pour représenter des nombres plus grands (16 bits, 32 bits, 64 bits, etc.) il faut décider de la manière de disposer ces octets multiples en mémoire.

4 octets sont utilisés pour représenter un nombre de 32 bits

Little endian est de loin l’option la plus couramment utilisée. Dans ce cas, les positions de valeur des octets en mémoire restent les mêmes à mesure que le nombre d’octets utilisés pour représenter le nombre augmente.

Le terme endian provient du roman de 1726 ‘Les voyages de Gulliver’, dans lequel il y a un conflit entre des sectes de Lilliputiens selon qu’ils cassent la coquille d’un œuf à la coque par son extrémité la plus petite ou la plus grande.

Copyright Labcenter Electronics Ltd. 2024

Traduction française

Copyright Multipower France 2024