Routage des boitiers BGA

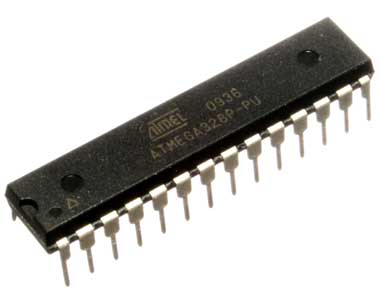

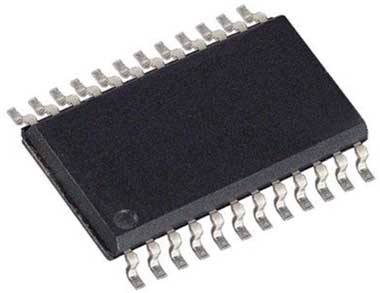

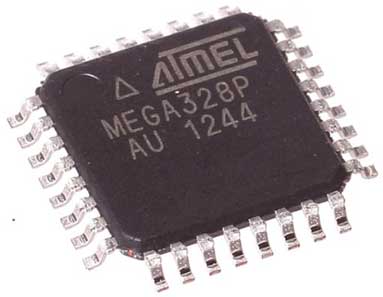

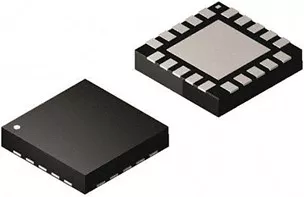

Lorsqu’un circuit intégré est découpé de la tranche de silicium, il peut être conditionné de plusieurs façons pour obtenir un boitier, notamment :

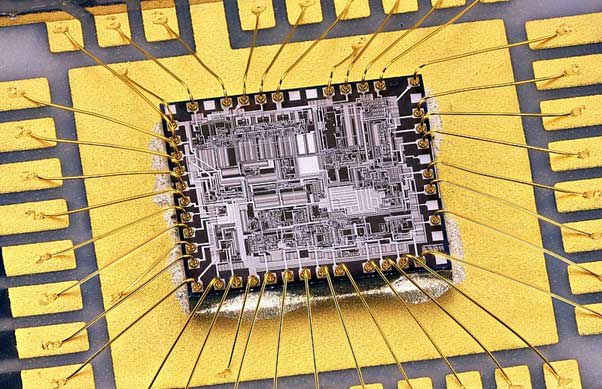

À l’intérieur des différents boîtiers en plastique, des connexions sont établies entre le circuit intégré en silicium et les broches du boîtier à l’aide d’une technique appelée ‘Wire Bonding’ en anglais.

Les boîtiers DIP sont plus grands et plus faciles à souder à la main (ce qui les rend plus adaptés aux amateurs), tandis que les boîtiers BGA ne peuvent pas être soudés à la main et nécessitent un équipement spécial pour être assemblés sur un circuit imprimé (PCB).

Les boîtiers BGA ont la plus grande densité de broches, ce qui signifie qu’ils occupent le moins d’espace sur le circuit imprimé, ce qui est essentiel pour la plupart des produits électroniques haut de gamme modernes (comme les smartphones). Cependant, avoir des boîtiers à si haute densité signifie que des techniques spéciales sont nécessaires pour acheminer tous les signaux sur le circuit imprimé.

Voici quelques conseils généraux concernant le routage des puces BGA lors de la conception de circuits imprimés (PCB).

Règles de conception

La première étape, avant même de commencer la disposition du PCB, consiste à décider des règles de conception, notamment :

- Combien de couches comportera la carte ?

- Quelle est la largeur minimale des pistes ?

- Quel est l’espacement minimal entre les pistes ?

- Quelle est la taille minimale des vias (diamètre de perçage minimum et anneau annulaire minimum) ?

En général, un nombre accru de couches et des tolérances de fonctionnalités plus serrées facilitent le routage de la carte. Cependant, il est important de noter que davantage de couches et des tolérances plus strictes entraînent généralement des coûts de fabrication plus élevés et des délais de production plus longs.

Volume de production

L’un des facteurs décisionnels est le volume de production envisagé – combien de ces cartes prévoyez vous de fabriquer ? Pour les produits en grande quantité, il peut être utile de déployer des efforts supplémentaires pour router soigneusement en utilisant le moins de couches possible afin de réduire le coût par carte de circuit imprimé. En revanche, pour les produits en faible quantité, le coût de main-d’œuvre lié à l’ajout de temps pour réduire le nombre de couches n’est pas justifiable.

Il est également nécessaire de vérifier quelles sont les capacités de votre fabricant de PCB et de déterminer s’il peut réellement produire une carte avec les spécifications que vous concevez, c’est-à-dire quelles sont leurs spécifications minimales en termes de largeur de piste, d’espacement entre les pistes, de taille de perçage et d’anneau annulaire (ainsi que le nombre maximum de couches de carte qu’ils peuvent produire).

Exigence d’impédance

Un autre facteur à prendre en compte est la nécessité d’impédances spécifiques et de savoir si certaines (ou beaucoup) des pistes nécessitent des impédances particulières. Les largeurs des pistes, les espacements entre les pistes et la disposition des couches détermineront l’impédance des pistes. De plus, il va sans dire que certaines des couches internes de la carte seront des plans de référence d’alimentation (pour une impédance constante). Veuillez consulter nos articles sur la conception haute vitesse pour plus d’informations si vous n’êtes pas déjà familiarisé avec ces concepts.

Certains BGA, tels que les unités de microprocesseur (MPU), comportent plusieurs tensions d’alimentation, et le ou les plans d’alimentation sur la ou les couches internes de la carte seront normalement divisés en différentes sections en fonction des connexions d’alimentation utilisées dans une zone particulière de la puce. Par exemple, la mémoire DDR peut fonctionner à une tension spécifique et aura un plan d’alimentation couvrant la puce DDR ainsi que la section DDR de l’unité MPU, tandis que la section SD/eMMC fonctionnera à une tension différente et aura son propre plan d’alimentation couvrant cette mémoire et cette section de l’unité MPU.

Avoir le bon plan d’alimentation sous les broches pertinentes est important pour l’ajustement d’impédance, mais facilite également le routage de ces broches car tout ce qu’elles nécessitent est une traversée (via) jusqu’au plan d’alimentation (plutôt qu’une piste routée à l’extérieur de la zone BGA).

Documentation du composant

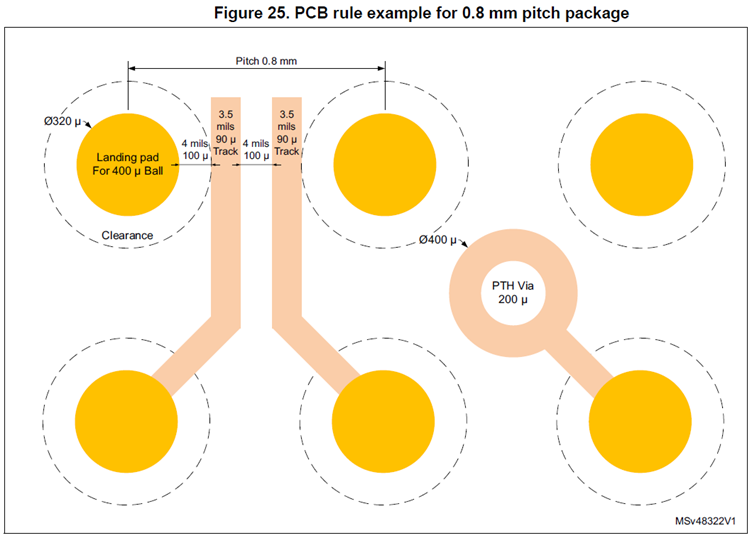

Parfois, la fiche technique du circuit intégré (IC) fournira des recommandations concernant certaines des règles de conception, comme cet extrait de la note d’application de ST Microelectronics sur le STM32MP1, qui donne des conseils pour commencer la conception matérielle pour ce processeur :

En général, il est toujours essentiel de consulter la documentation du composant pour connaître les exigences ou recommandations de conception. Il peut également y avoir des contraintes de conception spécifiques pour le routage de certaines sections du design, telles que les exigences d’impédance et d’espacement sur les connexions DDR.

Lors de l’importation de modèles de composants de bibliothèques dans la conception de circuits imprimés, il est utile de vérifier la taille du pad de réception BGA (BGA landing pad) des pièces importées. En règle générale, cette taille devrait représenter 80 % du diamètre de la bille BGA. Cependant, ce paramètre n’est pas toujours défini comme tel sur les empreintes importées, il est donc recommandé de vérifier et d’ajuster si nécessaire.

Les puces BGA nécessiteront presque toujours des condensateurs de découplage et éventuellement des résistances de calibration placées à proximité de la puce (généralement directement en dessous). Par conséquent, décider de la taille du boîtier pour ces composants est également une étape importante qui devrait être effectuée à l’avance. Encore une fois, plus la taille du boîtier est petite, plus le routage sera facile, mais plus les équipements et processus nécessaires à l’assemblage du PCB seront avancés (et donc potentiellement plus coûteux).

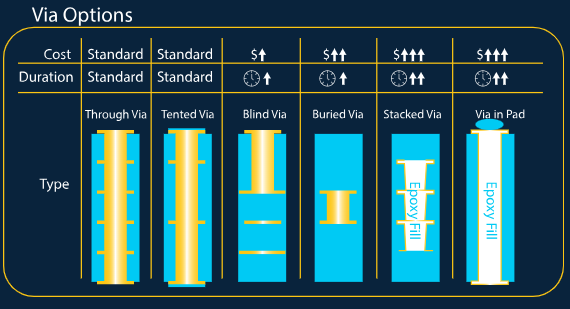

Options relatives aux vias

Une autre décision potentielle de conception concerne l’utilisation de vias borgnes et/ou enterrés, qui sont à nouveau plus coûteux mais facilitent également les conceptions de plus haute densité (ou les rendent même possibles). Les technologies de vias dans les pastilles (Via-in-pad) sont une autre technique qui peut être utilisée pour augmenter la densité, mais encore une fois, à un coût plus élevé.

Les vias remplis de résine, également appelés vias borgnes remplis ou vias enterrés remplis, sont des composants spécifiques dans la conception de circuits imprimés (PCB).

Découvrez comment traiter les vias remplis de résine dans Proteus ici

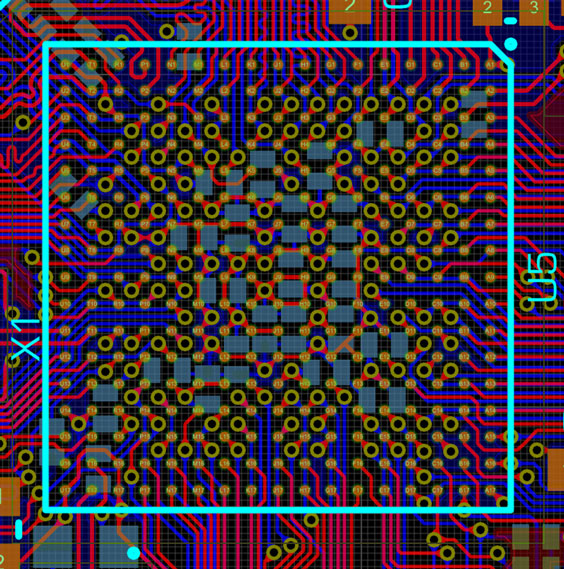

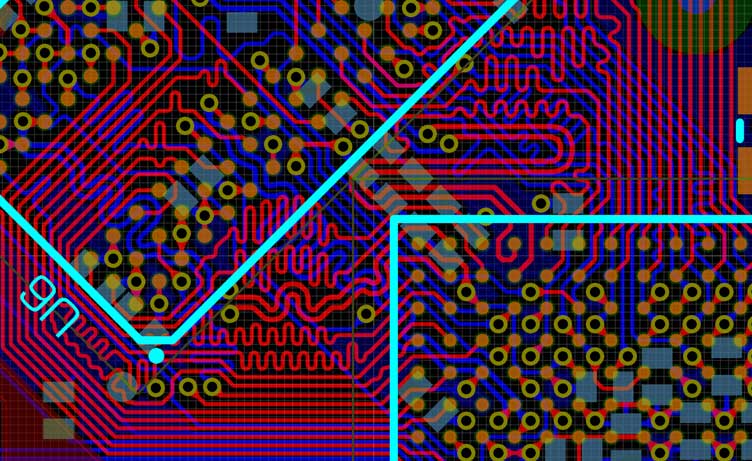

Placement des pistes

Une autre source à vérifier lors de la décision des règles de conception est le(s) circuit(s) de conception de référence pour la puce. Peu importe le logiciel de conception de PCB utilisé, les fabricants fourniront généralement les fichiers Gerber du circuit imprimé, qui peuvent être ouverts et inspectés à l’aide de logiciels de visualisation Gerber tels que ViewMate. Le nombre de couches, les largeurs des pistes, les espacements entre les pistes et les dimensions des vias peuvent tous être vérifiés de cette manière.

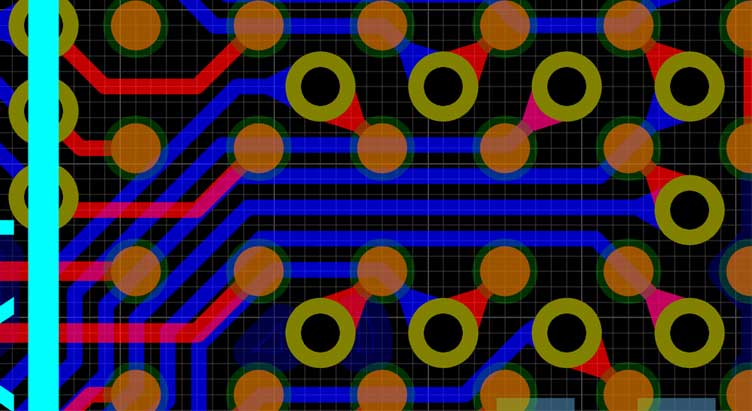

Certaines puces BGA (Ball Grid Array) ont des billes (balls) sélectivement peuplées, ce qui signifie que certaines positions de billes sur le BGA ne sont pas utilisées afin de créer des canaux d’échappement pour le routage des pistes.

Supprimer les pads non fonctionnels sur les vias de couches internes peut contribuer à libérer plus d’espace pour le routage, notamment lors de l’utilisation de cartes à six couches ou plus. Cela peut être particulièrement utile pour optimiser l’utilisation de l’espace et faciliter le routage des pistes dans des conceptions de circuits imprimés complexes.

Les pads non fonctionnels, également appelés pads fictifs ou pads thermiques, sont des zones sur une carte de circuit imprimé (PCB) intentionnellement laissées non connectées ou sans aucune fonction électrique.

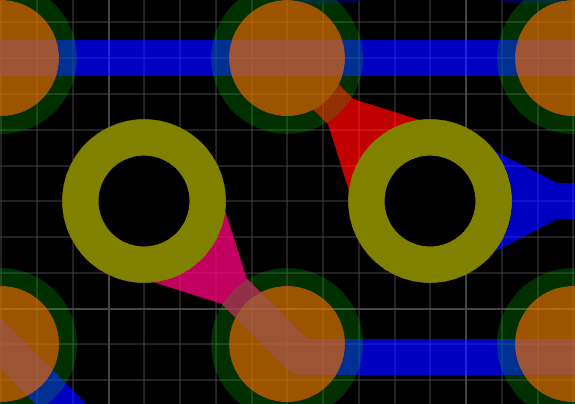

Les vias sont généralement disposés selon le motif appelé « dog bone » (os de chien) : configuration qui facilite le routage des pistes à partir des billes du BGA vers d’autres parties du circuit imprimé.

Une technique pour augmenter la densité des pistes échappées des rangées internes consiste à organiser les vias de manière à créer un canal où plusieurs pistes peuvent être routées en proximité étroite :

Comme dernier conseil, il peut parfois être utile de ne pas placer des composants couplés (comme une MCU et une DDR) trop près l’un de l’autre pour laisser suffisamment d’espace aux pistes à appairer en longueur par serpentins car elles peuvent prendre plus d’espace que l’on pourrait penser.

Copyright Labcenter Electronics Ltd. 2024

Traduction française

Copyright Multipower France 2024